## **An MCU/DSP Balancing Act**

Choosing the right solution

# Cut Development Time

Using In-Circuit Emulators and BDM's

#### **Macros**

- · Macro debug capability

- · Project support

- · Command line

- . Shadow RAM support

- . Single step in your macro

- · GUI capable macros

#### **Key Features**

- Real-time emulation at maximum chip speeds

- · High level support for popular C compilers

- · Advanced tracing capabilities

- · Configurable user interface with remote hookup capability

- High speed connection to PC through parallel port (LPTx) or plug-in ISA card

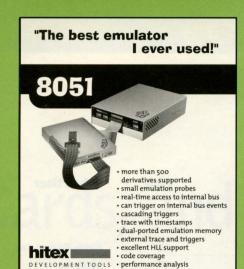

Nohau Supports These Microcontroller Families 8051 80C196 683xx 68HC11 P51XA ST10 MCS296 MCS251 68HC16 C166 68HC12 M16C

# www.nohau.com

51 East Campbell Avenue, Campbell, CA 95008 Phone: 1-888-88NOHAU (1-888-886-6428) Fax: 408-378-7869 E-mail: sales@nohau.com

visionICE

visionCLICK

visionPROBE

**Embedded Support Tools Corporation**

#

The New IDE for the New Millennium

- · New and Improved GUI

- · Graphical Browser

- · On-Line Help

- Syntax Coloring and Auto Indenting

- Simulator

- Version Control

- C++ Debugging

- EventAnalyzer

- · Project Builder

- Code Coverage

- · Run-Time Error Checking

- · Profiling

The Best Compilers.

The Best Debuggers.

Now, all wrapped up in a brand new, powerful, easy to use IDE. Once you try MULTI 2000, you won't want to struggle with "old fashioned" tools ever again. Contact us now for a start the millennium Free Evaluation CD and

with a bang!

# contents

JANUARY 2000

#### **Cover Story**

### Overlaps between Microcontrollers and DSPs

Though traditionally earmarked for different applications, DSPs and MCUs are crossing over into each other's territories.

BY BILL GIOVINO

#### Data Memory Paging Management

Mapping logical registers to physical registers requires the management of paged data memory. This twopart article explains a method to detect any potential paging errors in assembly programs.

BY HUGH O'BYRNE

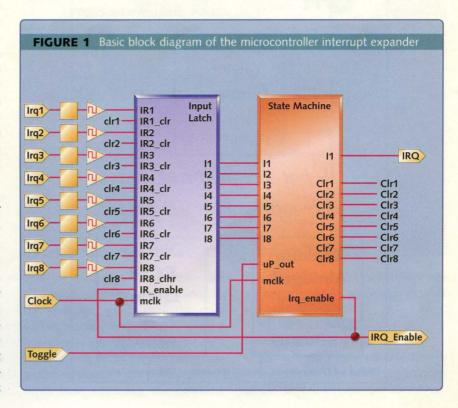

### How to Increase Interrupts in an MCU Design

In this article, the author looks at how a hardware/software co-design solution can stretch a given processor's usefulness. He describes an interrupt controller with a serial interface for microcontrollers.

BY RICHARD WALL

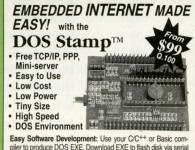

### internet appliance design

#### CONNECTING...

#### Slow and Steady Never Lost the Race

Embedded programmers aren't smarter than their PC counterparts—but they *are* more cautious. This column is also the final installment in a three-part series on checksums.

BY MICHAEL BARR

#### Embedding TCP/IP

In this second installment, the author discusses the details of putting TCP/IP into a resource-constrained embedded system.

BY TOM HERBERT

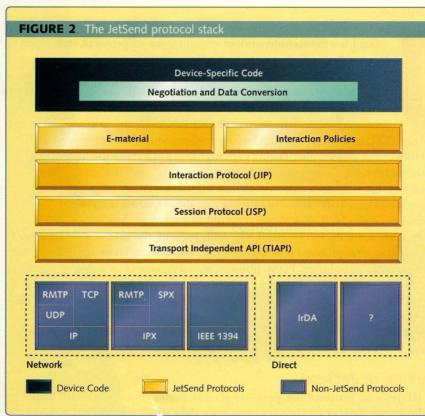

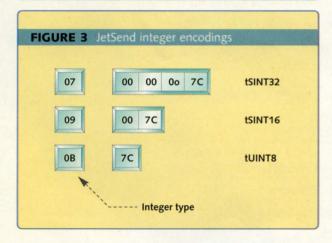

#### An Introduction to the JetSend Protocol

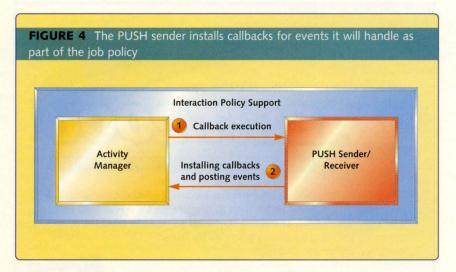

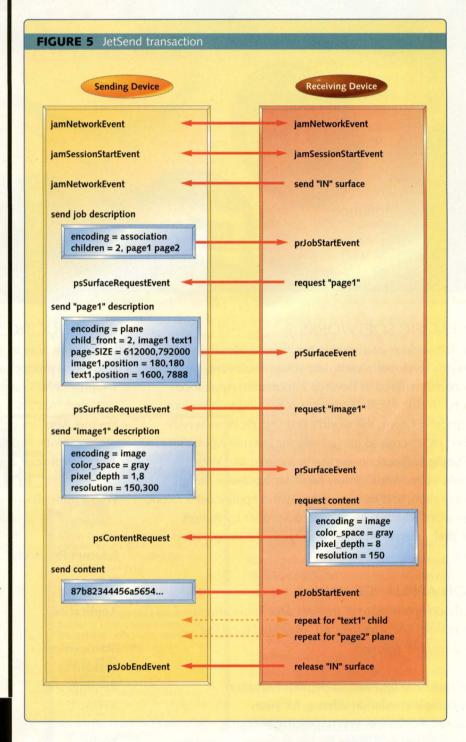

This article provides an overview of JetSend, a mediaindependent communications protocol that can exchange information in its proper context without any product-specific knowledge or device drivers. BY JOHN MEADOWS

82

A serial output interrupt expander can stretch an MCU's usefulness.

#### columns

- 7 PROGRAMMER'S TOOLBOX Maximizing Rigor BY JACK W. CRENSHAW

- 71 PROGRAMMING POINTERS

More on Overloading with const

BY DAN SAKS

- 87 SPECTRA

Simple and Effective

BY DON MORGAN

- 97 BREAK POINTS

Cores, Cards, and Tubes

BY JACK G. GANSSLE

- 100 STATE OF THE ART

What Barely Works

BY P.J. PLAUGER

#### departments

- 5 #INCLUDE

Entertaining Times

BY LINDSEY VEREEN

- 90 RECRUITMENT

- 92 MARKETPLACE

- 96 ADVERTISER INDEX

## "Microtek in-circuit emulators gave me more features and the best value."

You want to do it right, and meet project deadlines. That's not easy, especially when your debug environment includes RTOS and C++ support. And more hardware hides deeper inside silicon.

You can't escape these challenges, and neither can we. That's why we pack more features and interoperability into our emulators.

Only Microtek emulators offer integrated state analysis with clock-cycle time stamping – a traditional logic analyzer feature. This allows you to track down the causes for system crashes that are impossible for a software debugger to find. At the same time, we have integrated high-level source display... the kind logic analyzers can only show with a complicated connection to the target, multiple tool interfaces and non-interactive, post-processed source display.

You can quickly view executed code coverage from your emulator without a separate tool interface, and without instrumenting your code or maintaining separate builds. Plus, now you can run your Microtek emulator from any seat on the network.

No other emulator offers integrated state analysis. No other emulator offers our advanced trace and trigger system. No other emulator offers SWAT™Software Analysis Tools.

While other emulator companies are de-emphasizing their emulator business, we continue to innovate. This means you can choose the performance options you need – from entry-level to the most advanced in the industry, all at competitive prices.

#### MICROTEK IN-CIRCUIT EMULATORS

1 (800) 886-7333 www.microtekintl.com

Phone: (503) 533-4463 Fax: (503) 533-0956

Email: info@microtekintl.com

#### Call for a Free AppNote on these topics:

- 1. Using Microtek Emulators with WindRiver's Tornado™

- 2. How to Emulate a Single Target System on a Network 3. Instruction-Level Execution and Branch Code Coverage

- 4. Emulator Integrates Logic Analyzer State Analysis and High Level Trace

#### **Support**

for the following processors:

NEW Low Voltage Pentium<sup>o</sup> Pentium<sup>o</sup> II

Pentium<sup>®</sup>

Intel486<sup>™</sup>

Intel386™EX/CX/SX

Intel 186/188

683xx/HC16

8051/52/251

Financing Options Available

### **Entertaining Times**

II Co where are the flying cars?" asks Imy son Brad, who was raised on bright promises for the new millennium. He expected everyone to be zipping around in an airborne vehicle by this time. Come to think of it, so did I, based on prophecies I was fed a generation earlier. I suppose if the future were easier to predict, we would all have long since made killings in the stock market. What with the vagaries of prognosticating, and since Jeanne Dixon is not in my direct bloodline, I'm not about to make any predictions for the new millennium that would set me up for future ridicule. Instead I'll play it safe and limit myself to noting a few things that may be worth watching in the coming months and years.

For example, how much longer will Moore's Law be in effect? We can assume that semiconductor technologies will continue to reduce transistor size for a while at least, making transistors cheaper and more plentiful. Sooner or later, though, the laws of physics will call a halt to the incredible shrinking transistor. The maneuvers to postpone reaching this limit should prove worth watching.

The machinations in the development tools and RTOS business should provide plenty of entertainment as well. We've seen the first stages of consolidation, most recently with the acquisitions of ISI by Wind River and Cygnus Solutions by Red Hat. How many more mergers will follow?

Will changes in design methodologies brought about by increasing software content in electronic systems and shorter market cycles lead to new tools to support new design methodologies? What will be the impact of executable models in embedded software development? What's the likelihood of actually generating production code with a push of a button? As new tools evolve and gain acceptance, it will be interesting to see if the companies that produce them will be swallowed by the larger tools companies, or whether they will instead grow to compete with these companies.

Microsoft should offer some amusement of its own. Will it be split up, and if so will the disparate parts thrive? What, if anything, will become of Windows CE? Just watching Microsoft jockey for position in the post-PC era ought to give us hours of diversion.

The open source phenomenon should also prove intriguing. Will this trend continue, and if so, what will be its impact for embedded software developers? What will its effect be on software licensing models and on the companies that thrive on license revenues?

Consolidation among the singleboard computer companies is also something to watch for. Several mergers have already occurred during the past year or so, and we may see more. Will any companies be left standing besides Motorola and Solectron when the dust settles?

The rate at which bandwidth is increasing is often compared to Moore's Law. Will bandwidth continue to double at the same rate transistors do? What changes will this increase bring about?

Although it may be a curse to say "may you live in interesting times," I suspect that we are at least in for some entertaining times—almost as amazing as flying cars actually appearing in our local automobile showrooms. But no predictions.

lvereen@mfi.com

Vereen lyereen@mfi.com

MANAGING EDITOR

Michael Shapiro, mshapiro@mfi.com

TECHNICAL EDITOR

Michael Barr, mbarr@mfi.com (410) 796-1888

SPECIAL PROJECTS EDITOR Tarita Whittingham, twhittingham@mfi.com

ASSISTANT EDITOR

Felisa Yang, fyang@mfi.com

CONSULTING TECHNICAL EDITORS

Jack G. Ganssle Jerome L. Krasner, PhD

CONTRIBUTING EDITORS

Jack W. Crenshaw Larry Mittag Don Morgan

VICE PRESIDENT/ELECTRONICS

Donna J. Esposito

EMBEDDED/DSP GROUP DIRECTOR

**PUBLISHER** Eric Berg, (415) 278-5220

CALIFORNIA SALES MANAGER

CALIFORNIA SALES ASSISTANT

WESTERN ACCOUNT EXECUTIVE

Craig Hammond, (415) 278-5294

SALES ASSOCIATE, RECRUITMENT

EASTERN REGIONAL SALES MANAGER

EASTERN SALES

PRODUCTION COORDINATOR

CIRCULATION MANAGER

CIRCULATION DIRECTOR

SUBSCRIPTION CUSTOMER SERVICE

Non-U.S. subscribers: (847) 647-8602 embedded@halldata.co

embedded@naildata.com Back issues may be purchased on a pre-paid basis through: Miller Freeman, 1601 West 23rd St., Suite 200, Lawrence, KS 66046; (800) 444-4881; (785) 841-1631

Sherry Bloom. (415) 808-3980

EXECUTIVE PRODUCER, EMBEDDED.COM

ONLINE PRODUCTION COORDINATOR

CEO/MILLER FREEMAN WORLDWIDE

CHAIRMAN/MILLER FREEMAN INC.

PRESIDENT Donald A. Pazour

EXECUTIVE VICE PRESIDENT/CFO

**EXECUTIVE VICE PRESIDENTS** Darrell Denny C Regina Starr Ridley

SENIOR VICE PRESIDENTS

SENIOR VICE PRESIDENT/PRODUCTION

VICE PRESIDENT/CIRCULATION

Jerry M. Okabe

#### – Conventional RTOS? …sorry!

# OSE THE NEW GENERATION RTOS!

#### **FASTER**

Streamlined for extreme reliability and speed, OSE's kernel and TCP/IP stacks blow away the competition. From the RTOS to the tools, OSE sets tomorrow's standards for small size and high performance.

#### **TOUGHER**

As the only fault-tolerant RTOS, OSE supports mission-critical real-time systems, allowing complete non-stop recovery from hardware and software failures AND hot swaps – critical for high-availability functionality.

#### LONGER-LASTING

OSE is heterogeneous, scalable, and distributable, protecting your investment by allowing your application to grow from one CPU to hundreds.

#### **MORE POWERFUL**

OSE's kernel offers automatic supervision, dynamic reconfiguration and integrated error handling, letting you focus on your core competency: designing applications.

#### SIMPLER

OSE's powerful ultra-efficient message-based architecture lets you write nearly every bit of application code using only eight system calls.

#### SAFER

OSE is the world's only RTOS that is safety certified to the demanding specifications of IEC 61508 . OSE is also being certified according to the stringent DO 178-B.

#### **PROVEN**

Millions of products worldwide are already taking advantage of OSE, including the top brands in telecommunications and process control. OSE is the RTOS of the future.

www.enea.com

Jack W. Crenshaw

# Maximizing Rigor

A funny thing happened on my way to last month's column: I discovered that I wasn't being rigorous enough. The only saving grace is that it seems that neither has anyone else.

If you read the column ("More on Minimization," December 1999, p. 7), you'll recall that we were talking about ways to seek a minimum of a function, by dividing a given segment into smaller segments. You might also recall that I got seriously bogged down when I reached the question of what to do if the old minimum and all the new probes all yield the same value.

At the time, I offered a solution, which does seem to get us out of trouble most of the time. However, it doesn't satisfy me because it doesn't improve the situation. That is, we haven't gotten any closer to the new minimum, and in fact, might be moving away from it. The only hope is that the new geometry will somehow lead to a better result on the following iterations.

Looking back into the distant past, I now remember that this is why I've never looked very deeply into methods for minimizing functions. I kept running into this potential problem, and didn't see any obvious way out of it. What threw me on this one is that nobody else who has published algorithms seemed to be particularly bothered by the possibility that I've described. I've read almost all the books ever written on computer algorithms, and I've never seen anyone express much concern that the question would ever come up. Certainly, I've seen more than one implementation of one of the most popular and ubiquitous methods for minimizing functions of a single

scalar variable, and not one of them deals with the problem as a special case.

One reason I keep mentioning the different, but similar, problem of finding the root of a function is that I admire the robustness which almost all solutions offer. If a function is continous, once a root has been bracketed by any of these methods, losing it is impossible. That root *will* be found, in time.

I want a minimization technique

I've ever done in this column. Rest assured that before we're done, we will have looked at virtually every reasonable algorithm for both scalar and vector (multivariate) arguments. But we must learn to walk before we learn to run, and sometimes it's a good thing to try to squeeze as much information out of simpler methods before moving on to the big time. Please be patient; we'll get there.

# Through the use of a more rigorous approach, Dr. Crenshaw digs himself out of a minimization quagmire.

that is equally robust, and works even when the function being used is pathological. So far, we don't have that. It's this lack of robustness, I now realize, that's been bothering me. Last month, I offered a suggestion as to how to get out of the box, but as I said, it doesn't satisfy. In retrospect, I've decided not to leave it at that. I've decided that we will not continue until I've found a method that *does* meet my standards for robustness. So that's what we'll do this month.

Some of you, especially those readers who are already knowledgeable about methods for minimizing functions, may be wondering when I'm going to stop tinkering around with simple interval-halving schemes, and get to the better known and faster methods that you and I both know exist. To those, I would say, fear not. This series is probably going to be the most extensive and intensive series

#### The problem

For the benefit of newcomers, we've been looking at the problem of finding the minimum of some function f(x). Last month, we were looking at a method where we begin with three equally spaced points, the middle of which has a lower value of f(x) than the outer points. The search method involves probing the function at two new points, which split both intervals. If either of these points yields a lower value of f(x), we take this as the new minimum, and reduce the size of the search region. If neither of them is smaller than the original midpoint, we move the boundaries in. Either way, we have the minimum captured and inexorably reduce the boundaries of our search. Eventually, we draw a noose around the minimum we seek.

The point where I got stuck was: what do we do if the value of f(x) is

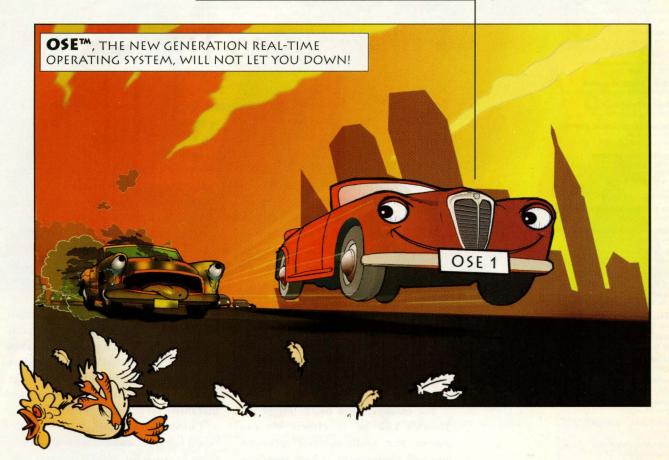

### Countless individual internet appliances.

| Imaging            | Internet Appliances | Internet Infrastructure |

|--------------------|---------------------|-------------------------|

| Telecommunications | Intelligent I/O     | Wireless                |

| Aerospace/Defense  | Automotive          | Industrial Control      |

### One common element.

In the booming market of Internet appliances, success is all about time-to market, cost and product differentiation. If you design to win in that environment, there's one company with whom you'll definitely see eye to eye — Wind River Systems.

With our Tornado embedded development tools and VxWorks real-time operating system, you'll have a huge head start in your product development cycle. Our open, reliable

architecture will allow you to differentiate your product for any sized design, all the way from the end-user application code to the look and feel of the graphical user interface.

By utilizing Wind River technology, Liberate Technologies (formerly known as NCI) rolled out its interactive TV software across Europe and the US, and TeraLogic, Inc. successfully launched its Cougar Reference Platform for HDTV. With over 200 Java design wins,

we've also made Java work in the embedded market. And our Universal Graphics Layer (UGL) provides a solid foundation for graphics development in the embedded space.

Find out more about Tornado and VxWorks. Visit www.wrs.com/html/espgene.html or call 1-800-545-WIND. Then give your designs the advantage of Wind River Systems. Because your competition is so fierce, you can't afford to blink first.

equal at all three inner points? How do we decide which one of these points to take as the new middle point?

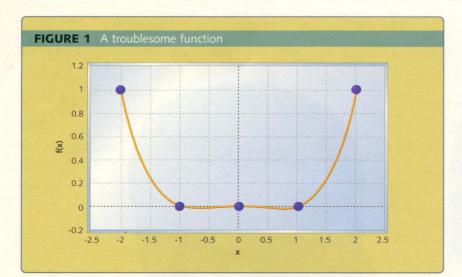

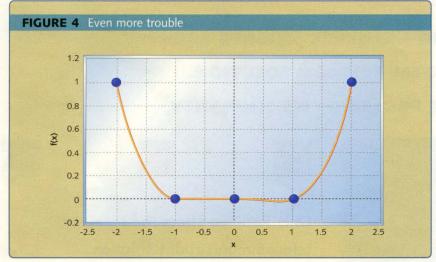

You might be thinking, "But is this really a realistic case? Are there really functions that behave this way?" You bet there are. Here's one that does so, over the range -2..2:

$$f(x) = \frac{1}{12}x^2(x^2 - 1) \tag{1}$$

The function, which is shown in Figure 1, certainly seems simple enough. It's hardly what one would call pathological. But as you can see, either from the graph or the equation itself, it absolutely must be equal to zero at x = -1, 0, and 1.

Imagine that we began the search

with the three points x = -2, 0, and 2. These are satisfactory points, since the middle point is clearly lower than the other two. So, proceeding with our algorithm of halving the intervals, we probe at x = -1 and x = 1. Rats! All three inner points are equal, and we are stuck.

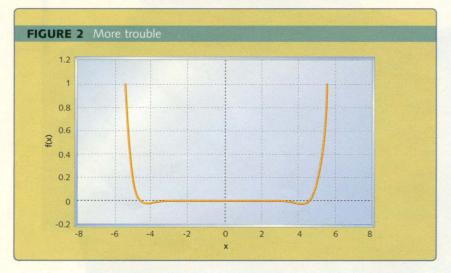

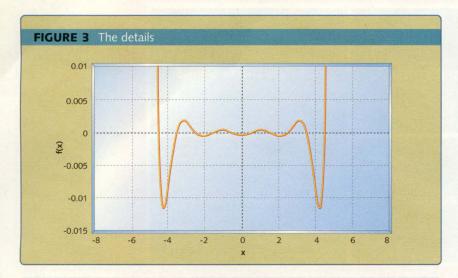

Some years ago, I thought maybe I could get out of this box by continuing to subdivide the intervals. I suppose that might work, but it might also take a while. If you think the function of Figure 1 is tough, consider this one:

$$g(x) = \frac{1}{3! \cdot 5! \cdot 7!} \left[ x^2 - \left(\frac{1}{2}\right)^2 \right] \left[ x^2 - \left(\frac{3}{2}\right)^2 \right]$$

$$\left[ x^2 - \left(\frac{5}{2}\right)^2 \right] \left[ x^2 - \left(\frac{7}{2}\right)^2 \right] \left[ x^2 - \left(\frac{9}{2}\right)^2 \right]$$

I've shown this function in Figure 2, and again, with the region around the xaxis blown up, in Figure 3. This function has no less than ten inner points that yield the same value for f(x). Though it's true that I had to construct these two functions to make my point, it's by no means certain that we won't encounter just these same functions, or ones like them, in the real world. The last function makes it clear that we won't be able to escape the problem by simply dividing the interval into more parts.

#### Which way out?

Let's take another look at Figure 1. We can see that the desired minimum is somewhere around x = -0.7. A little calculus, in fact, will show us exactly where it is:

$$\frac{df(x)}{dx} = \frac{1}{6}x(2x^2 - 1)$$

(3)

The function is stationary when its derivative is zero. In this case, we have three possibilities. One is when x itself is zero. But that one turns out to be a local maximum, as the figure plainly shows. The two minima are given by solving:

$$2x^2 - 1 = 0 (4)$$

which gives:

$$x = \pm \frac{\sqrt{2}}{2} = \pm 0.70711 \tag{5}$$

Remember, we've already decided that in the presence of the possibility of multiple roots, we'd prefer to home in on the left-hand one. Therefore x =-0.70711 is the solution we seek. But how to find it?

It's tempting to say that if the function is high at  $P_1$  (x = -2 in our example), and low at  $P_2$  (x=-1), it must be heading south when it gets there. Therefore a minimum must exist in the region between P2 and P3, and we'd be safe to pull in  $P_5$  to make the range -2..0. That approach would indeed bracket the minimum for our example, and lead to

WIDE AREA NETWORKING INTEL CPU PLATFORM SYSTEM PLATFORMS **DSP TECHNOLOGIES**

### HERE'S A NO-NONSENSE MESSAGE ABOUT OUR TOTAL TELECOM SOLUTION. DON'T BE FOOLED BY ITS SIMPLICITY.

#### Only RadiSys offers the total telecommunications solution.

A solution this complete is hard to pull off. A lot of vendors offer different parts of telecom solutions. Only RadiSys has the vision and technical expertise to deliver the total, integrated solution across both PCI and CompactPCI architectures. RadiSys has acquired Texas Micro, and is now positioned to redefine how the market is buying OEM embedded telecommunications systems. Now you can let us put the total solution together. Download our comprehensive white paper on SS7, and find out how simple it is to get the total solution from one source at www.radisys.com, or call 1-877-837-6859.

State of the art Pentium solutions for

Enterprise and carrier class CompactPCI and PCI system enclosures and backplanes

WIDE AREA NETWORKING

Field-proven frame relay, SS7, ATM, T1/E1, X.25, IP and other protocols and interfaces

**DSP TECHNOLOGIES**Advanced TI C6x voice processing solutions-hardware and algorithms

Download FREE white paper today! www.radisys.com/SS7

the correct solution. But look at where this would lead us. After the change in range, we are left with the points:

- $P_1 = (-2,1)$

- $P_3 = (-1,0)$

- $P_5 = (0,0)$

P<sub>3</sub> and P<sub>5</sub> now have equal y-values, and our requirement that the three points always have distinct values, with P3 being strictly the lowest, has been violated.

The fact that this approach would indeed have resulted in a good solution for this example is immaterial. We can't go by the results of a single example, and I'm not willing to risk the success of the method on the fact that I think I know what the shape of the function is. Are you?

If you have any doubt that this

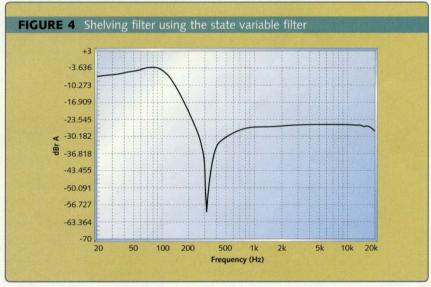

approach is a Bad Idea, you need only take one look at Figure 4, where I've modified the function only slightly. In this (admittedly artificial, but still normal looking and perfectly feasible) function, the minimum on the right is the only one present. By moving P5 in to P<sub>3</sub>, we would miss it completely, and the minimum would have neatly slipped from our grasp.

Last month, I suggesting taking the leftmost of the equal points, P2, as the new middle point, and leaving the two end points alone. That was done with the attitude that we have to do something to make future iterations more successful than our current one. By throwing off the symmetry of our first step, I was hoping to rattle the cage of the minimum enough to frighten it out of hiding. In this case, that move would leave us with the three points:

- $\bullet$  P<sub>1</sub> = (-2,1)

- $P_3 = (-1,0)$

- $P_5 = (2,1)$

At least we have maintained our requirement that the value of f(x) at P<sub>3</sub> remain strictly lower than at the two end points. The approach does, however, have three weaknesses:

- It does not reduce the width of the search area, which we'd like to do at every step

- It leaves us with an asymmetric set of points; the intervals are no longer equal

- It will eventually find the wrong solution

While it's true that no method short of an exhaustive search can guarantee finding the left-most of multiple solutions, it would certainly be nice if our approach didn't fail to do so on only our second test function.

What's more, we have seen that we can have many more than three points with equal y-value. Given any such interval-halving method, what would you like to wager that I can't come up with a function that will hit equal values long enough to drive the method crazy?

Two conclusions seem to be coming clear. First of all, we're probably going to have to abandon the desire to keep our intervals balanced, so that the middle point is halfway between the other two. That desire was already violated by the suggestion just discussed, and it is likely to be unsupportable in general. That conclusion, in and of itself, is important because it leads to a pretty robust and popular method you'll be seeing next month.

The second conclusion is that we need to do something besides halving intervals to help us break out of the equal-value box. We need to do something radical. That something comes from dropping the idea of halving altogether, or at least temporarily.

# ASICUS Programmabus.

rue to its namesake, Spartan™ FPGAs remain synonymous with "a commitment to winning", regardless of the challenge. And armed with that spirit, Xilinx delivers the Spartan-XL family.

The Spartan-XL architecture offers an easy-to-use alternative to traditional ASICs plus the added flexibility and time-to-market advantages inherent in a programmable logic solution.

Ranging in density from 5K to 40K system gates, the Spartan-XL family features on-chip dual port synchronous RAM, while it's 100+MHz performance and flexible I/O structure make it ideally suited for 32 bit 33MHz PCI applications. All this and more for under \$2.50\*.

From price to performance, feature set to software, the Spartan-XL device family was born and bred to meet the challenge.

### www.xilinx.com

#### **LISTING 2** Minimizing via bisection

```

/* Perform one step of a minimization by double

* bisection. Input required is three points, of

* which the middle one is strictly smaller.

* The points need not be evenly spaced.

* Function includes protection from equal values

void bisect(double (*f)(double), double &xO, double &yO,

double &x2, double &y2,

double &x4, double &y4){

// x1 wiggle factor

double r = 0.95:

// Bisect the first interval

double x1 = (x0+x2)/2:

double y1 = f(x1);

// Better take care of problem case first

// Also, better have a way out!

int i = 20;

while((y1=y2)&& (i>0)){

x1 = r*x1 + (1-r)*x0;

y1 = f(x1);

-i;

if(i=0)

cout << "bisect: cannot find new x1\n";

// if new point is lower,

// use as new middle

if(y1 < y2){

x4 = x2;

y4 = y2;

x2 = x1;

y2 = y1;

return;

// if it's higher, move in left limit

if(y1 > y2){

x0 = x1;

y0 = y1;

// Bisect the second interval

double x3 = (x2+x4)/2;

double y3 = f(x3);

// if new point is lower,

// use as new middle

if(y3 < y2){

x0 = x2;

y0 = y2;

x2 = x3;

y2 = y3;

return;

```

#### **Breaking out**

The way out of the box is to think of continuous functions, rather than sampling at specific points. Taking another look at Figure 1, we can see that, while the function has multiple crossings of the x-axis and multiple extrema, the slope at Po is nonzero. If we had available to us the slope of the function, as well as the function itself, we would know immediately that a minimum sits between x = -1 and x = 0. We would also know exactly how to arrange further probing values. As a matter of fact, in future columns we'll look at methods that use the analytical slope of the function, as well as its value.

Lacking the analytical slope, is there any way we can tell what to do to get a better set of bracketing points? As a matter of fact, there is: we can sense the slope by "wiggling" one of the points slightly. When we do this, three things can happen:

- The value of f(x) doesn't change

- The value goes down

- The value goes up

In either of the last two cases, we now have a value that's different from the original midpoint. We choose whichever set of points gives us a bracketing condition, and we're out of the box. In the event that the function doesn't change, we must try again, by moving the point (or a different one) some more.

The next questions we should be asking are: which point do we wiggle, and in which direction? Addressing the first point, I think you can see that wiggling the middle point, P3, is not such a good idea. In the example of Figure 1, that point is a stationary, local maximum, so its slope is zero, at least locally. In Figure 4, the slope is identically zero on the left, all the way to P2. The last thing we want to do is to merge the two points; that would take us right back to the "left-most of equal points" scheme, which we have already seen doesn't work all that well.

Moving either of the end points, P<sub>1</sub> and P<sub>5</sub>, is a terrible idea. They are our fences, our bulwarks holding in the elusive minimum. I am not about to move

UNTIL NOW, JAVA FOR EMBEDDED SYSTEMS HAS BEEN JUST TOO BIG AND UNPREDICTABLE.

You want the power of Java. But for your embedded application, it's just too hefty, unpredictable, and not fast enough. Insignia Solutions introduces Jeode, our implementation of Java, which is fully compliant with Sun's EmbeddedJava specification and uniquely designed for embedded systems. Jeode lets you optimize size, performance and predictability for your specific embedded application.

Featuring our proprietary EVM" (Embedded Virtual Machine"), Jeode is highly configurable and tunable to achieve optimal performance in resource-constrained embedded systems. The EVM provides adaptive optimizing dynamic compilation for fast execution and concurrent garbage collection for predictable behavior. With more than a decade of delivering virtual machines, Insignia Solutions is already providing Jeode to Fortune 500 makers of networking equipment, PDAs, mass storage systems, consumer electronic devices and more. So, can Java be small enough, fast enough and predictable enough for your embedded system? The answer is a resounding yes! With Jeode. Call 1.800.848.7677 or visit www.insignia.com.

```

LISTING 2, continued Minimizing via bisection

// if it's higher, move in right limit

if(y3 > y2){

x4 = x3;

y4 = y3;

/* Solve for minimum of function, using n successive bisections.

* Initial points _MUST_ represent legal configuration, i.e.,

* y0 > y1, y2 > y1.

* The points need not be evenly spaced.

double minimize(double (*f)(double), double &xO, double &yO,

double &x1, double &y1,

double &x2, double &y2, double eps){

// protection from infinite loop

int i = 30;

while((fabs(x2-x0)>eps)&&(i>0)){

bisect(f, x0, y0, x1, y1, x2, y2);

if(i=0)

cout << "iteration failed" << endl;

return x1;

void main(void){

double x0 = 0;

double y0 = f(x0);

double x1 = 0.5;

double y1 = f(x1);

double x2 = 1;

double y2 = f(x2);

cout << minimize(f, x0, y0, x1, y1, x2, y2, 1.0e-6);

```

them until I know for certain that I have better places to which I can move them.

That leaves us with P2 and P4, and since we're going to concentrate on finding the left-most of multiple minima, we'll choose P2.

Now we have the question: which way do we move it? It's no good trying to move it to the right; that would get us in the same trouble as moving P3 to the left. Eventually, the two points could merge. On the other hand, moving P<sub>9</sub> to the *left* is a great idea.

Consider this: we know that the height of  $P_1$  is higher than that of  $P_2$ . We also know that the function is (or is supposed to be) continuous. If we move P2 leftwards, we eventually approach P1 closer and closer, and the function absolutely has to eventually give up a y-value closer to that of P<sub>1</sub>. It has no choice.

Of course, the minimum could be between P<sub>1</sub> and P<sub>2</sub>, so the point could move down instead of up. That's okay. We don't really care which way it moves. Any vertical motion at all distinguishes P2 from P3, and we will have enough information to reorder the points.

So here, in a nutshell, is our algorithm, which is about as robust as I can think of:

- 1. Given three points  $P_1$ ,  $P_3$ , and  $P_5$ , with P3 strictly lower than the other

- 2. Generate P<sub>2</sub> by bisecting the inter-

- 3. If P<sub>2</sub> is the same height as P<sub>3</sub>, force it either higher or lower by moving it towards P1

- 4. If  $P_2$  is higher than  $P_1$ , replace  $P_1$  by

- 5. If P<sub>9</sub> is lower than P<sub>3</sub>, replace P<sub>5</sub> by P<sub>3</sub>, and P<sub>3</sub> by P<sub>2</sub>

- 6. Generate P<sub>4</sub> by bisecting the interval P<sub>3</sub>..P5

- 7. If  $P_4$  is higher than  $P_5$ , replace  $P_5$  by

- 8. If P<sub>4</sub> is lower than P<sub>3</sub>, replace P<sub>5</sub> by P<sub>3</sub>, and P<sub>3</sub> by P<sub>4</sub>

- 9. Repeat until done

There remain only the issues of deciding what we mean by "move P2 towards P<sub>1</sub>" and "done."

As for the moving, I favor reducing the distance between P<sub>1</sub> and P<sub>2</sub> by a fixed ratio, r. That is, let:

$$x_2' = x_1 + r(x_2 - x_1)$$

=  $rx_2 + (1 - r)x_1$  (6)

Each step moves P2 towards P1, and it approaches P<sub>1</sub> asymptotically, but it never actually gets there, so we needn't worry about the points merging.

To decide when we're done, the usual criterion is to measure the distance from P<sub>1</sub> to P<sub>5</sub> and stop when we feel that it's small enough. The only other alternative I can think of is to keep a record of past values of  $x_3$ , and stop when two successive values are nearly equal. This makes me nervous, though, since I can envision cases where  $x_3$  doesn't move much, and yet the minimum is still not pinned down.

A word of warning: don't expect to be able to pin down the minimum as tightly as you're used to pinning down, say, a root of a function or a polynomial. In the end, as we get closer to the minimum, every continuous function looks like a parabola, and the tighter we pull in the range, the flatter the parabola becomes. If you try to push the technology too far, it's possible to get into the range where the parabola looks like a straight line or, worse yet, a noisy discontinuous function, dominated by floating-point roundoff error. A good rule of thumb is to avoid narrowing the range down lower than several times the square root of the resolution you can expect in f(x).

# Windows CE is pumping gas.

Radiant

At twelve gallons of gas per minute, you need a robust operating system to keep track of every drop of inventory. Radiant Systems and Tokheim know that real time is the only time for gas pumps. They know that Microsoft® Windows® CE is the real time embedded operating system. They proved that Microsoft Windows CE can track gas to one thousandth of a gallon.

Your customers demand reliable, customized, network-ready devices yesterday. Get an operating system that delivers. Microsoft Windows CE is powerful, modular, connected. And developers are familiar with its Win32® API. That's why Windows CE was chosen by Radiant Systems to power the electronics for Quantium, Tokheim's line of fuel dispensers.

Windows CE brings the power and flexibility of the familiar Win32 API to the embedded world. Now you can use the world-class desktop API anywhere. That's why Radiant Systems, Tokheim, and other leading embedded developers are selecting the Windows CE operating system. With a community of over five million Windows programming developers, a plethora of core operating system services and sample code, you'll find the resources you need.

Windows CE supplies you with a comprehensive mix of communication and connectivity options. Sophisticated security like CHAP, SSL, and Digital Certificates. Internet protocols and a world-class Web browser with dynamic HTML, cascading style sheets, and JScript® software.

Win the race to market. Power your next generation of intelligent devices with Windows CE.

Visit www.microsoft.com/windowsce/embedded

ere do you want to go today?\* Microsoft\*

Using these principles, I've written a new version of our function minimize(), designed to locate even the most elusive minimum. The code is shown in Listing 1. Except for the wiggling of P2, and the new halt condition based upon the interval, it's pretty much the same as you saw last month. I've added some protection for infinite loops. Trust me, they are necessary, as I found out the hard way. If you make the new error criterion, eps, too small, our wiggle logic breaks down because all the function values are equal. Without the loop count, the wiggle loop will run forever.

You'll note that I've resorted to two error messages in case things go wrong. Normally, I try to avoid error messages since we're supposed to be talking about software suitable for embedded systems. In this case, however, we absolutely need to have some way of knowing if the search procedure failed to converge. For use as an example, the error message approach is okay. In a true real-time system, you would surely have some other mechanism, such as a status word, to report error conditions. Such a mechanism is far too implementation-specific for me to use it here, so we'll have to take error messages and live with them.

#### Where do we go from here?

Let's take a moment to review where we've been, and speculate as to where we're going. To find the minimum of a function f(x), we began with a simple approach that simply divided an initial interval into N points, evaluated all N of them, and took the lowest as the solution. That method was certainly effective—it's the only one guaranteed to find a global minimum, so don't discard it as being too primitive. But it's also slow, and gets slower as we try to improve accuracy.

We made one simple improvement to that approach, which was to skip out of the loop after finding the first minimum (thereby destroying the method's ability to find the global minimum, but also gaining speed).

Our next approach was to seek to speed things up by requiring fewer evaluations of the function f(x). Instead of searching the entire search space with fine resolution, we started out with a rather course search (10 points), and used that to narrow down the region to search for the next step. Calling this function allowed us to iteratively refine the estimate of the minimum.

Last month and this month, we have managed to reduce the number of points in a given search from 10 to five. We built an algorithm that worked last month, and we got one that was robust this month. The obvious next question is: can we reduce the number of points even further?

The answer is yes. We can't reduce it to three; we've already been down that road, and learned that it's bad practice to throw out any point until we're absolutely sure we have improved the situation at every step. We can, however, reduce the number of points to four.

Recall that the current algorithm bisects both intervals—the one from P<sub>1</sub> to  $P_3$ , and from  $P_3$  to  $P_5$ —in a single pass. This turns out to be unnecessary. With our newfound ability to deal with equalheight cases, we can be sure that each interval is reduced in size on each pass. Given that, we can alternate between P<sub>3</sub> and P<sub>5</sub>, bisecting (or otherwise dividing) each interval on alternate passes. That reduces the number of points we must maintain to four: three passed in and out, and one used internally to narrow the search.

We'll look at that technique next month. In the process, we'll (re)discover the famous Golden Ratio search, which will benefit as much from our equalvalue fix as the current algorithm does.

See you then.

Jack W. Crenshaw a senior principal design engineer at Alliant Tech Systems Inc. in Clearwater, FL. He holds a PhD in physics from Auburn University. Crenshaw enjoys contact and can be reached via email at jcrens@earthlink.net.

Pure Java<sup>™</sup> based RTOS for embedded systems

#### Be fast

Jbed runs faster than other Javas because it always compiles, never interprets.

#### Stay small

Jbed's small memory footprint (starting from 8 kBytes) allows for low-cost hardware with less memory.

#### Save time and cost

Jbed offers the productivity advantage of the Java language to the embedded world.

#### Features included

- Integrated Development Environment

- Deadline-driven, time-triggered scheduling with admission testing

- Incremental Garbage Collector compliant with hard real-time

- Reflection, serialization

- All standard communication protocols supported

- Hot-loading with esmertec's TBCC (target byte code compiler)

- Y2K compliant

Jbed

Hard RTOS and JVM in one!

esmertec inc., Technoparkstrasse 1, CH-8005 Zürich, Switzerland, www.esmertec.com, info@esmertec.com, F +41 1 445 37 30, X +41 1 445 37 34

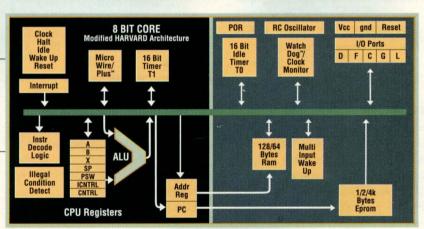

# Overlaps Between Microcontrollers and DSPs

Microcontollers are primarily used in applications that are interrupt-driven, sensing and controlling external events. You can usually find DSPs in systems that require the precision processing of analog signals. This article describes how traditional DSP and MCU applications are crossing over into each other's territories.

ntel developed the 4004 microprocessor in 1971 for the Busicom desktop calculator (remember when a calculator took up a desktop?) and sold it for \$200 a chip. It ran at 92.5kHz internally. Intel's initial strategy was to use this device to sell more memory chips. It was an unexpected success, and was quickly followed by a flurry of similarly enhanced devices from Intel, Motorola, Zilog, and Texas Instruments. Key to the success of the later devices were features like on-chip memory, I/O ports, and hardware peripherals, enabling these chips to economize PC board space in control-oriented applications.

In the past 15 years, digital signal processing has been seen as a specialized segment of an embedded development marketplace dominated by microcontrollers. Digital signal processors (DSPs) were initially used in highly specialized segments where precision processing of analog signals could not be accomplished effectively using conventional analog circuit components. In 1982, the first DSP, the Texas Instruments TMS32010, proved that this segment existed by combining specialized hardware for accelerating multiplication with a Harvard (dual bus) memory architecture, introducing the architectural enhancements that would be found on later digital signal processors.

Years after the introduction of the two architectures, speculation continues on whether a convergence can ever take place. Techniques are debated, architectures compared, and positions promoted. Many articles and papers have been written on this topic—and you're reading one of them now. The difference is that here I will discuss hardcore, real-world selection criteria, including time to market, track records of semiconductor companies, and quality of development tools.

#### The players

Deeply embedded microcontrollers are primarily used in control-oriented applications that are interrupt driven,

#### Traditional DSP applications are as subtle as a freight train—they are brute force mathematical applications, pure and simple.

sensing and controlling external events. The external environment is detected either by digital I/O, interrupt pins, or analog (A/D) inputs. The source of the signals to these pins comes from switches, analog and digital sensors, and status signals from other systems. Each input represents a piece of information on the status of some outside event. Outputs are sent to actuators, relays, motors, or other drivers that control events. In between is the trusty microcontroller, analyzing the inputs and the present state of the system, determining when to switch on and what to turn off. The software that does all this, that makes these decisions, does so in a mostly conditional fashion; that is, conditional jumps and bit manipulation and shifts are the staples of embedded control ("interrupts" is counted as a condition here—program flow is altered on the occurrence of an external event).

DSPs, meanwhile, are traditionally found in systems that require the precision processing of digitized analog signals. The performance goal of a DSP architecture is to perform as many arithmetic operations as possible in the smallest number of cycles. Traditional DSP applications are as subtle as a freight train—they are brute force mathematical applications, pure and simple. Traditional DSPs use complex, compound instructions that allow the programmer to perform multiple operations with a single instruction cycle and increase the amount of useful processing done. For example, most are able to compute one tap of an FIR filter in a single cycle. DSP cores are crafted to be number crunchers, and to that end they must do two things well: first, a DSP core must perform multiple math functions, including multiplication, extremely quickly and second, a DSP

needs to continuously feed the data path to the number-crunching computational units (so that they can continue to crunch away). It is pursuit of this functionality that makes the programming model of a DSP look so different when compared to a microcontroller. See Table 1 for more details.

#### Size matters

Note that in Table 1, the benefits of the hardware features of microcontrollers translate into reduced code size and reduced board space—two issues critical to cost efficiency in embedded applications. Reduced code size results in smaller on-chip memory area; the denser the code, the smaller the chip die area. After all, the semiconductor business is, at its base, a real estate business where the cost is about \$300 million per acre. Faster execution is also a decision point, but is more important now than before. By contrast, the benefits of DSP hardware features result in faster execution and improved data throughput. Code size has traditionally not been as significant as execution speed, but this too is changing. (I'll describe this in more detail later.)

Control-oriented systems have traditionally utilized only a microcontroller, but some embedded applications add a DSP accessible to the microcontroller's external memory space to speed processing of math-oriented tasks. Examples include digital

|                                                             |                                                                    | Marie Control of the |

|-------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TABLE 1 Summary of                                          | embedded processor archite                                         | ctural comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TABLE 1 Summary of                                          | embedded processor archite                                         | etara companson                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Microcontroller<br>Efficiently resolve complex              | conditional control situations                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| System Requirement                                          | Feature                                                            | Benefit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| I/O control                                                 | I/O ports with bit-level control                                   | Efficient (quick, small code) control Direct interface to actuators, switches, and digital status signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Peripheral communications                                   | Serial ports: SPI, I <sup>2</sup> C,<br>MicroWire, UART, CAN       | Hardware support for expansion and external device communications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Precision control of actuators and motors                   | Sophisticated timers and PWM modules                               | Low software overhead control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Quickly resolve complex software program control flow       | Conditional jumps Bit test instructions Interrupt priority control | Efficient (quick, small code) program flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Fast response to external events                            | External interrupts Multiple interrupt levels                      | Program control immediately redirected on event occurrence; minimal overhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Conversion of sensor data                                   | Analog-to-digital converters                                       | Hardware support for external sensors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Digital signal processor<br>Deterministic software behavior | avior                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| System Requirement                                          | Feature                                                            | Benefit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

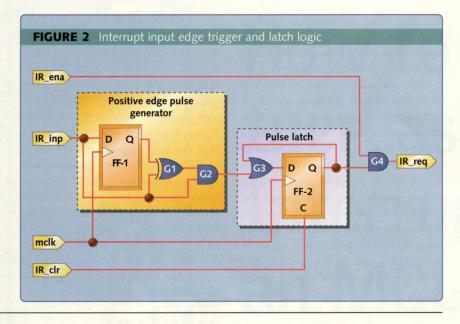

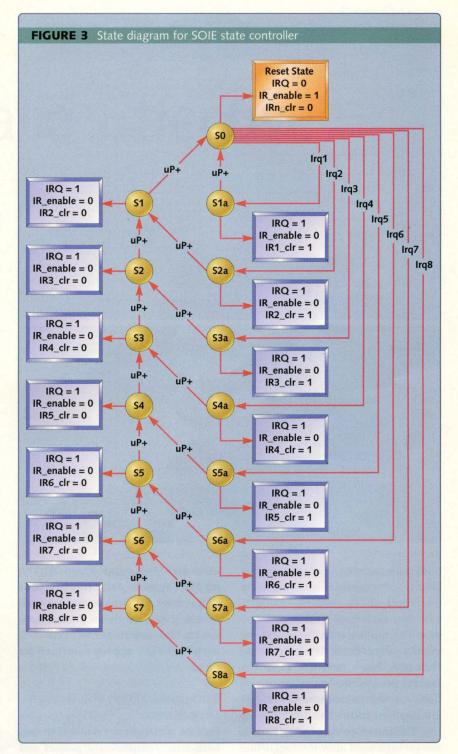

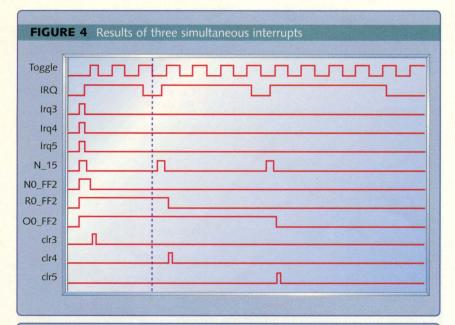

| Software filters                                            | Multiply/accumulate unit<br>Zero-overhead loops                    | Digital filtering in few cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |